#### **General Description**

The MAX9550/MAX9551/MAX9552 provide a VCOM source for TFT LCDs. The MAX9550/MAX9551/ MAX9552 source and sink a large current to quickly restore the VCOM voltage, making it ideal for TFT LCDs. The output settles to within 0.1% in less than 2µs. In addition, the MAX9550/MAX9551/MAX9552 directly drive the capacitive load in the VCOM layer of the TFT LCDs without the need for a series resistor.

The MAX9550/MAX9551/MAX9552 feature single, dual, and guad channel VCOM amplifiers, respectively. The MAX9550/MAX9551/MAX9552 can drive up to 800mA of peak current per channel and operate up to 20V. The devices feature soft-start to reduce inrush current, output short-circuit protection, and thermal shutdown.

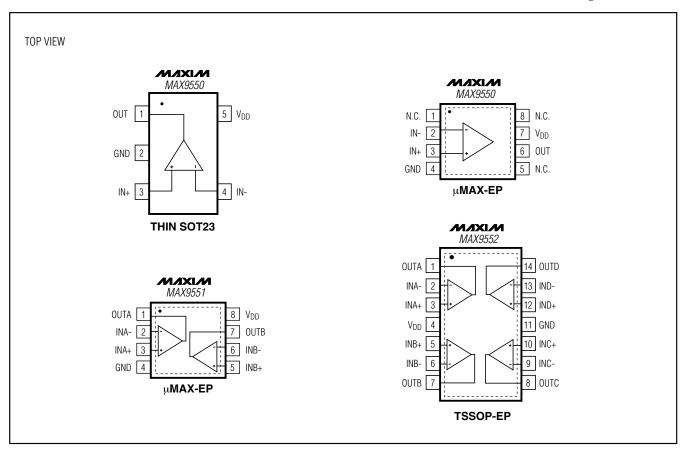

The MAX9550 is available in a space-saving 5-pin thin SOT23 package, and an 8-pin µMAX® package with an exposed paddle. The MAX9551 is available in an 8-pin µMAX package with an exposed paddle. The MAX9552 is available in a 14-pin TSSOP package. All devices are specified over the -40°C to +85°C temperature range.

#### **Applications**

**TFT-LCD Panels** Instrument Control Voltage Sources

Pin Configuration appears at end of data sheet.

# Features

- ♦ Operates Up To 20V

- ♦ 800mA Peak Output Current

- ♦ Settles to Within 0.1% of Vout in Less than 2µs

- **♦ Excellent Load Regulation**

- ♦ Thermal-Shutdown Protection

- ♦ Short-Circuit Protection to Both Rails

- ♦ Soft-Start to Reduce Inrush Current

### **Ordering Information**

| PART         | AMPS | PIN-PACKAGE    | PKG<br>CODE | TOP<br>MARK |  |

|--------------|------|----------------|-------------|-------------|--|

| MAX9550EZK+T | 1    | 5 Thin SOT23-5 | Z5-1        | ADSG        |  |

| MAX9550EUA+  | 1    | 8 μMAX-EP*     | U8E-2       | AABA        |  |

| MAX9551EUA+  | 2    | 8 μMAX-EP*     | U8E-2       | _           |  |

| MAX9552EUD+  | 4    | 14 TSSOP-EP*   | U14E-3      | _           |  |

Note: All devices specified over the -40°C to +85°C operating temperature range.

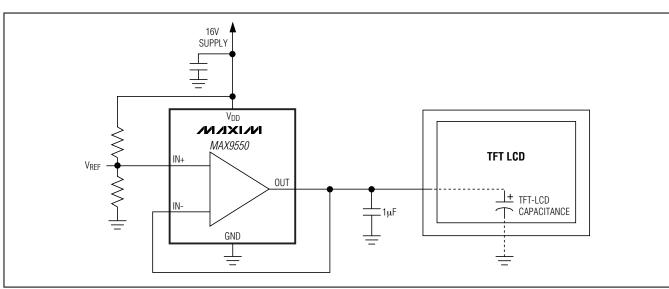

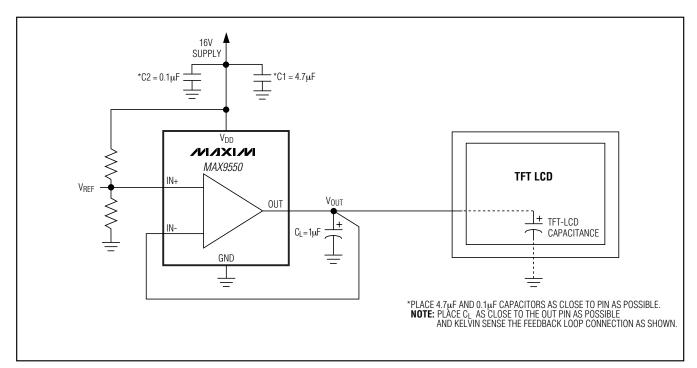

## **Typical Operating Circuit**

μΜΑΧ is a registered trademark of Maxim Integrated Products, Inc.

MIXIM

Maxim Integrated Products 1

<sup>+</sup>Denotes lead-free package.

<sup>\*</sup>EP = Exposed paddle.

#### **ABSOLUTE MAXIMUM RATINGS**

| Supply Voltage (VDD to GND)        | 0.3\/ to +32\/          |

|------------------------------------|-------------------------|

| 117 0 ( 22 )                       |                         |

| Any Other Pin to GND               | 0.3V to (VDD + $0.3$ V) |

| IN+/IN- (current)                  | ±20mA                   |

| OUT, OUT_ (current)                | 1A                      |

| Continuous Power Dissipation (TA = |                         |

| 5-Pin Thin SOT23 (derate 2.7mW/    | °C above +70°C)219.1mW  |

| 824.7mW      |

|--------------|

| )1667mW      |

| 0°C to +85°C |

| +150°C       |

| °C to +150°C |

| +300°C       |

|              |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

$(V_{DD}=16V,~GND=0V,~V_{CM}=V_{OUT}=V_{DD}$  / 2,  $C_L=1\mu F,~T_A=T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $T_A=+25^{\circ}C$ .) (Note 1)

| PARAMETER                    | SYMBOL                                                   | CONDITIONS                                                                         |                                   | MIN | TYP                   | MAX                   | UNITS |  |

|------------------------------|----------------------------------------------------------|------------------------------------------------------------------------------------|-----------------------------------|-----|-----------------------|-----------------------|-------|--|

| DC CHARACTERISTICS           |                                                          |                                                                                    |                                   |     |                       |                       |       |  |

| Supply Voltage Range         | V <sub>DD</sub>                                          | Inferred from PSRR test and transient load test                                    |                                   | 7   |                       | 20                    | ٧     |  |

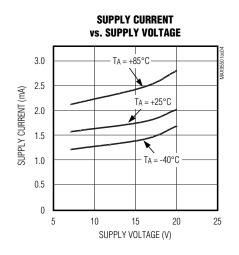

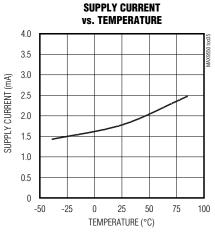

| Quiescent Current            | Icc                                                      | Per channel                                                                        |                                   |     | 2                     | 4                     | mA    |  |

| Low Output Voltage           | V <sub>OL</sub>                                          | $I_L = -4mA$                                                                       |                                   |     | 0.04                  | 0.1                   | V     |  |

| High Output Voltage          | VoH                                                      | $I_H = +4mA$                                                                       |                                   |     | V <sub>DD</sub> -0.04 | V <sub>DD</sub> - 0.1 | V     |  |

| Input Offset Voltage         | Vos                                                      |                                                                                    |                                   | -10 | +1                    | +10                   | mV    |  |

| Input Bias Current           | ΙΒ                                                       |                                                                                    |                                   |     | 0.01                  | 1                     | μΑ    |  |

| Input Resistance             | RIN                                                      |                                                                                    |                                   |     | 1                     |                       | МΩ    |  |

| Common-Mode Input Voltage    | CMVR                                                     | Inferred from CMR                                                                  | R                                 | 2   |                       | V <sub>DD</sub> - 2   | V     |  |

| Common-Mode Rejection Ratio  | CMRR                                                     | $2V \le V_{IN} \le (V_{DD} - 2)$                                                   | 2V)                               | 80  | 96                    |                       | dB    |  |

| Power-Supply Rejection Ratio | PSRR                                                     | $V_{OUT} = 3.5V, V_{DD}$                                                           | = 7V to 16V                       | 80  | 96                    |                       | dB    |  |

| Continuous Output Current    | Io                                                       | V <sub>DD</sub> = 7V, V <sub>OUT</sub> = 3.5V, guaranteed by load, regulation test |                                   | 55  |                       |                       | mA    |  |

| Outrout Load Description     | 1.04                                                     | I <sub>OUT</sub> = 0mA to 50mA                                                     |                                   |     | 6                     | 13                    | \/    |  |

| Output Load Regulation       | tput Load Regulation LR1 I <sub>OUT</sub> = 0mA to -50mA |                                                                                    | mA                                |     | 6                     | 13                    | mV    |  |

| Output Load Pagulation       | LR2                                                      | V <sub>DD</sub> = 7V,<br>V <sub>OUT</sub> = 3.5V                                   | $I_{OUT} = 0mA \text{ to } -55mA$ |     | 6.5                   | 15                    | mV    |  |

| Output Load Regulation       | LNZ                                                      |                                                                                    | I <sub>OUT</sub> = 0mA to 55mA    |     | 6.5                   | 15                    | IIIV  |  |

| Thermal Shutdown             |                                                          |                                                                                    |                                   |     | +160                  |                       | °C    |  |

| Thermal Hysteresis           |                                                          |                                                                                    |                                   |     | 15                    |                       | °C    |  |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DD} = 16V, GND = 0V, V_{CM} = V_{OUT} = V_{DD} / 2, C_L = 1\mu F, T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .) (Note 1)

| PARAMETER                 | SYMBOL             | CONDITIONS                                                                                                                   |                                                               | MIN  | TYP  | MAX | UNITS |

|---------------------------|--------------------|------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|------|------|-----|-------|

| AC CHARACTERISTICS        | AC CHARACTERISTICS |                                                                                                                              |                                                               |      |      |     |       |

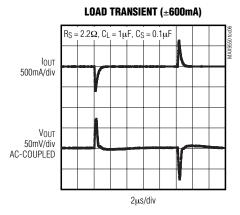

| Settling Time             | ts                 | Settling to 0.1% of $V_{OUT}$ , $I_L$ = 0 to 600mA, $C_L$ = 1 $\mu$ F, $R_S$ = 2.2 $\Omega$ , $C_S$ = 0.1 $\mu$ F (Figure 1) |                                                               |      | 2.0  |     | μs    |

| Input Capacitance         | C <sub>IN</sub>    |                                                                                                                              |                                                               |      | 1.5  |     | рF    |

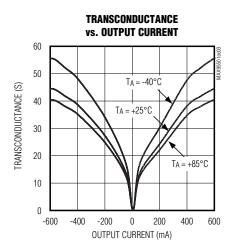

| Transconductance          | am                 | $I_{OUT} = \pm 50 \text{mA}$                                                                                                 |                                                               |      | 13   |     | S     |

| Transconductance          | gm                 | $I_{OUT} = \pm 500 mA$                                                                                                       |                                                               |      | 42   |     |       |

| Transient Outrout Ourrent | IOUTMAX            | A <sub>V</sub> = 1                                                                                                           | $V_{DD} = 7V$ , $V_{IN} = 1.5V$ pulse for 100 $\mu$ s         | ±200 | ±290 |     | - mA  |

| Transient Output Current  |                    |                                                                                                                              | V <sub>DD</sub> = 16V, V <sub>IN</sub> = 1.5V pulse for 100μs | ±600 | ±830 |     |       |

Note 1: All devices are 100% production tested at T<sub>A</sub> = +25°C. All temperature limits are guaranteed by design.

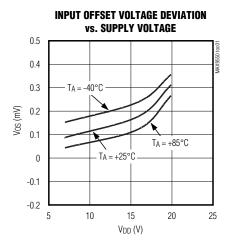

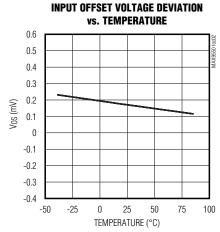

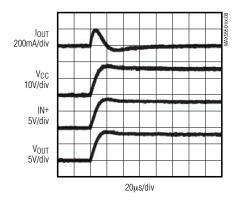

## Typical Operating Characteristics

$(V_{DD} = 16V, GND = 0V, V_{CM} = V_{OUT} = V_{DD} / 2, C_L = 1\mu F, T_A = +25^{\circ}C, unless otherwise noted.)$

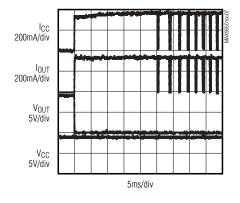

### **Typical Operating Characteristics (continued)**

$(V_{DD} = 16V, GND = 0V, V_{CM} = V_{OUT} = V_{DD} / 2, C_L = 1\mu F, T_A = +25$ °C, unless otherwise noted.)

#### **SHORT-CIRCUIT WAVEFORMS**

#### STARTUP WAVEFORM

## Pin Description

|               |         | PIN     |         |                   |                                                                       |  |

|---------------|---------|---------|---------|-------------------|-----------------------------------------------------------------------|--|

| MAX           | 9550    |         |         | NAME              | FUNCTION                                                              |  |

| THIN<br>SOT23 | μМΑХ    | MAX9551 | MAX9552 | NAME              | FUNCTION                                                              |  |

| 1             | 6       | _       | _       | OUT               | VCOM Output                                                           |  |

| 2             | 4       | 4       | 11      | GND               | Ground                                                                |  |

| 3             | 3       | _       | _       | IN+               | Positive Input                                                        |  |

| 4             | 2       | _       | _       | IN-               | Negative Input                                                        |  |

| 5             | 7       | 8       | 4       | $V_{\mathrm{DD}}$ | Positive Supply Input                                                 |  |

| _             | _       | 1       | 1       | OUTA              | VCOM Output A                                                         |  |

| _             | _       | 3       | 3       | INA+              | Positive Input A                                                      |  |

| _             | _       | 2       | 2       | INA-              | Negative Input A                                                      |  |

| _             | 1, 5, 8 | _       | _       | N.C.              | No Connection. Not internally connected.                              |  |

| _             | _       | 5       | 5       | INB+              | Positive Input B                                                      |  |

| _             | _       | 6       | 6       | INB-              | Negative Input B                                                      |  |

| _             | _       | 7       | 7       | OUTB              | VCOM Output B                                                         |  |

| _             | _       | _       | 8       | OUTC              | VCOM Output C                                                         |  |

| _             | _       | _       | 9       | INC-              | Negative Input C                                                      |  |

| _             | _       | _       | 10      | INC+              | Positive Input C                                                      |  |

| _             | _       | _       | 12      | IND+              | Positive Input D                                                      |  |

| _             | _       | _       | 13      | IND-              | Negative Input D                                                      |  |

| _             | _       | _       | 14      | OUTD              | VCOM Output D                                                         |  |

| _             | EP      | EP      | EP      | EP                | Exposed Paddle. EP is internally connected to GND. Connect EP to GND. |  |

### **Detailed Description**

The MAX9550/MAX9551/MAX9552 operational transconductance amplifiers (OTA) hold the VCOM voltage stable while providing the ability to source and sink a high current quickly (800mA typ) into a capacitive load such as the backplane of a TFT-LCD panel. The output settles to within 0.1% in less than 2µs. The fast settling time is achieved by increasing the transconductance of the buffer as the output current increases (see the *Typical Operating Characteristics*).

In addition, the MAX9550/MAX9551/MAX9552 directly drive the capacitive load in the VCOM layer of the TFT LCD without the need for a series resistor.

The MAX9550/MAX9551/MAX9552 unity-gain bandwidth is:

GBW =  $g_M / 2\pi C_{OUT}$

where C<sub>OUT</sub> is the capacitive load at the output and g<sub>M</sub> is the transconductance.

To insure buffer stability, place a  $1\mu F$  low-ESR capacitor as close to the OUT pin as possible. However, this value may be reduced if the TFT-LCD panel load provides some of the capacitance and the resistance in series when this capacitance is low. Connect the feedback at OUT using a Kelvin connection at the low-ESR capacitor.

#### Thermal Shutdown with Temperature Hysteresis

The MAX9550/MAX9551/MAX9552 are capable of high output currents and therefore, feature thermal-shutdown protection with temperature hysteresis. When the die temperature reaches +160°C, the devices shut down. When the die cools down by 15°C, the devices turn on again.

Figure 1. Settling Time Test Circuit

### Applications Information

#### **Output Load Capacitor**

The output load capacitor must have a low ESR value  $(50m\Omega \text{ or lower})$  and it must be placed as close as possible to the OUT pin to ensure buffer stability (see Figure 2). Ceramic capacitors are an excellent choice.

#### **Power Supplies and Bypass Capacitors**

The MAX9550/MAX9551/MAX9552 operate from a 6V to 20V single supply, or from  $\pm 3V$  to  $\pm 10V$  dual supplies. Proper supply bypassing ensures stability while driving high transient loads. The MAX9550/MAX9551/MAX9552 require minimum  $4.7\mu F$  (C1) and  $0.1\mu F$  (C2) power-supply bypass capacitors placed as close as possible to

the power-supply pin ( $V_{DD}$ ). See Figure 2. For dual-supply operation, use 4.7 $\mu$ F and 0.1 $\mu$ F bypass capacitors on both supplies ( $V_{DD}$  and GND) with each capacitor placed as close as possible to the  $V_{DD}$  and GND pins.

#### **Layout and Grounding**

The exposed paddle on the  $\mu$ MAX and TSSOP packages provides a low thermal resistance for heat dissipation. Solder the exposed paddle to a ground plane for best results. Do not route traces under these packages. For dual-supply operation, the exposed paddle (EP) must be electrically connected to the negative supply or it can be left unconnected.

Figure 2. Typical TFT-LCD Backplane Drive Circuit

### **Pin Configurations**

\_\_\_Chip Information

PROCESS: BICMOS

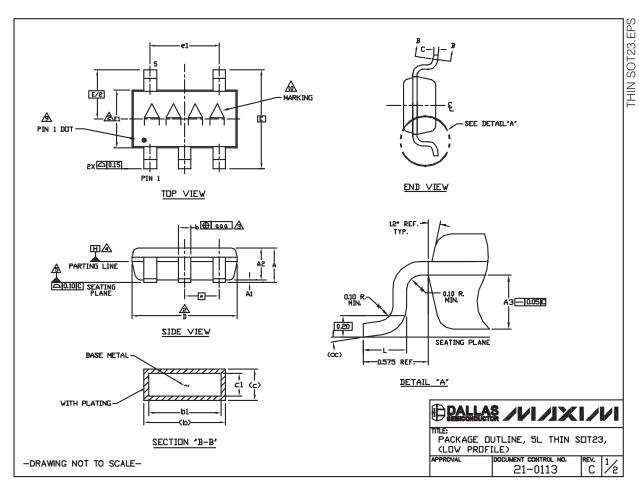

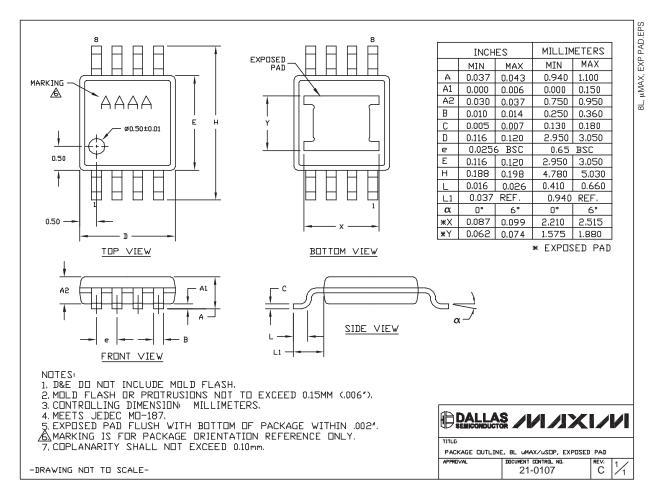

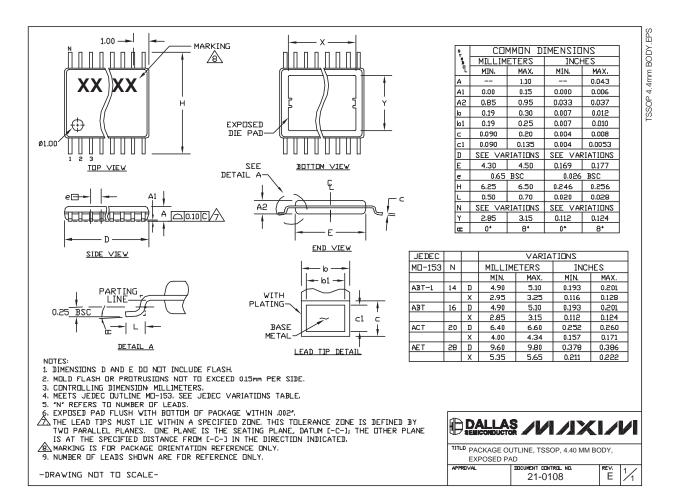

## **Package Information**

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information go to <a href="https://www.maxim-ic.com/packages">www.maxim-ic.com/packages</a>.)

#### Package Information (continued)

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information go to www.maxim-ic.com/packages.)

#### NOTES:

1. ALL DIMENSIONS ARE IN MILLIMETERS.

'D' AND "E1" ARE REFERENCE DATUM AND DO NOT INCLUDE MOLD FLASH OR PROTRUSIONS, AND ARE MEASURED AT THE BOTTOM PARTING LINE. MOLD FLASH OR PROTRUSION SHALL NOT EXCEED 0.15mm ON "D" AND 0.25mm ON "E" PER SIDE.

THE LEAD WIDTH DIMENSION DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.07mm TOTAL IN EXCESS OF THE LEAD WIDTH DIMENSION AT MAXIMUM MATERIAL CONDITION.

DATUM PLANE "H" LOCATED AT MOLD PARTING LINE AND COINCIDENT WITH LEAD, WHERE LEAD EXITS PLASTIC BODY AT THE BOTTOM OF PARTING LINE.

THE LEAD TIPS MUST LINE WITHIN A SPECIFIED TOLERANCE ZONE. THIS TOLERANCE ZONE IS DEFINED BY TWO PARALLEL LINES. ONE PLANE IS THE SEATING PLANE, DATUM (-C-I) AND THE OTHER PLANE IS AT THE SPECIFIED DISTANCE FROM (-C-I IN THE DIRECTION INDICATED. FORMED LEADS SHALL BE PLANAR WITH RESPECT TO ONE ANOTHER WITH 0.10mm AT SEATING PLANE.

- THIS PART IS COMPLIANT WITH JEDEC SPECIFICATION MD-193 EXCEPT FOR THE "e" DIMENSION WHICH IS 0.95mm INSTEAD OF 1.00mm. THIS PART IS IN FULL COMPLIANCE TO EIAJ SPECIFICATION SC-74.

- COPLANARITY APPLIES TO THE EXPOSED PAD AS WELL AS THE TERMINALS. COPLANARITY SHALL NOT EXCEED 0.08mm.

- 8. VARPAGE SHALL NOT EXCEED 0.10mm.

79. THE TERMINAL #1 IDENTIFIER AND TERMINAL NUMBERING CONVENTION SHALL CONFORM TO JESD 95-1 PP-012. DETAILS OF TERMINAL #1 IDENTIFIER ARE OPTIONAL. THE TERMINAL #1 IDENTIFIER MAY BE EITHER A MOLD OR MARKED FEATURE.

10 MARKING IS FOR PACKAGE ORIENTATION REFERENCE ONLY.

11. ALL DIMENSIONS APPLY TO BOTH LEADED (-) AND LEAD FREE (+) PACKAGE CODES.

| SYMBOLS                |          |          |      |  |  |

|------------------------|----------|----------|------|--|--|

|                        | MIN      | NDM      | MAX  |  |  |

| Α                      | -        | -        | 1.10 |  |  |

| A1                     | 0.00     | 0.075    | 0.10 |  |  |

| A2                     | 0.85     | 0.88     | 0.90 |  |  |

| A3                     |          | 0.50 BSC |      |  |  |

| b                      | 0.30     | -        | 0.45 |  |  |

| b1                     | 0.25     | 0.35     | 0.40 |  |  |

| c                      | 0.15     | _        | 0.20 |  |  |

| <b>c</b> 1             | 0.12     | 0.127    | 0.15 |  |  |

| D                      | 2.80     | 2.90     | 3.00 |  |  |

| E                      |          | 2.75 BSC |      |  |  |

| E1                     | 1.55     | 1.60     | 1.65 |  |  |

| L                      | 0.30     | 0.40     | 0.50 |  |  |

| e1                     | 1.90 BSC |          |      |  |  |

| е                      | 0.95 BSC |          |      |  |  |

| oc                     | 0*       | 4*       | 8*   |  |  |

| aaa                    | 0.20     |          |      |  |  |

| Pkg. codesi Z5-1j Z5-2 |          |          |      |  |  |

PALLAS /VI/IXI/VI

PACKAGE DUTLINE, 5L THIN SDT23, (LOW PROFILE)

DOCUMENT CONTROL NO. 21-0113 С

-DRAWING NOT TO SCALE-

### **Package Information (continued)**

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information go to <a href="https://www.maxim-ic.com/packages">www.maxim-ic.com/packages</a>.)

MIXIM

### **Package Information (continued)**

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information go to <a href="https://www.maxim-ic.com/packages">www.maxim-ic.com/packages</a>.)

## Revision History

Pages changed at Rev 3: 1, 2, 9, 10, 12

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

12 \_\_\_\_\_\_Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600